www.acsami.org Research Article

# Modulation Doping and Reduced Hysteresis in Monochalcogenide InSe/GaS Heterostructure 2D Field-Effect Transistors

Julian Ignacio Deagueros,\* Min Gao, Alice Cai, Xiaotong Li, Rajesh Kumar Ulaganathan, Shankar Mani, Raman Sankar, Hatsuo Ishida, and Xuan P. A. Gao\*

Cite This: ACS Appl. Mater. Interfaces 2025, 17, 35723-35731

**ACCESS** I

III Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Heterostructures made from 2D materials have led to the discovery of many new electronic phases and have the potential for electronic devices with better performance. However, the mechanism by which charge is transferred or distributed in these novel heterostructure devices made of atomically thin semiconductors is yet to be fully understood. By creating and electronically characterizing InSe/GaS heterostructure field-effect transistors with different metal contact configurations, we observed a decrease in the maximum on-current and an increase in the hysteresis when both the InSe and GaS layers are in contact with the metal contacts. This, combined with the time-dependent conductance decay measurements, suggests that charge flow into the GaS from the metal contacts is the source of the hysteresis, which can be mitigated by encapsulating the GaS with InSe. Our resultant nearly hysteresis-free devices exhibit an average field-effect mobility of  $34 \pm 8 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  at room temperature, comparable to that of bare InSe of the same size, with an average n-type modulation doping of  $\sim 1 \times 10^{12} \text{ cm}^{-2}$  from the GaS layer.

KEYWORDS: 2D field-effect transistors, van der Waals heterostructures, modulation doping, hysteresis, threshold voltage, on-current, field-effect mobility, carrier density

#### INTRODUCTION

Two-dimensional (2D) materials have garnered much interest in recent years due to their potential application in nano- $^{1-5}$  and opto- $^{6,7}$  electronics. Their novel physical properties,  $^{8,9}$  the ease with which one can fabricate intricate device structures,  $^{10-13}$  and the possibility of surpassing today's electronics' performance have made them a hot topic in academia.  $^{14,15}$  Much attention has been paid to transition metal dichalcogenides, particularly  $MoS_2$ , and their possible use as channel materials in field-effect transistors (FETs). However, progress toward achieving high-performance  $MoS_2$  FETs is limited by  $MoS_2$ 's large effective mass, large density of point defects and charged impurities, and phonon scattering.  $^{16-18}$

Despite their promising properties, integration of 2D materials with conventional oxide dielectrics often results in poor device performance (e.g., low or average mobility, <sup>3,19,20</sup> large hysteresis, <sup>21–23</sup> low on/off ratio, large subthreshold swing <sup>12,24,25</sup>). These effects have been attributed to the large density of scattering centers present at the semiconductor/dielectric interface, such as Coulomb impurities, charge traps, and defects, mainly from the oxide layer. <sup>26,27</sup> These results highlight the role of the semiconductor-dielectric interface quality on the performance of FETs.

In an attempt to mitigate this issue, different insulators have been used, from polymer-based<sup>28</sup> to high- $\kappa$  dielectrics, to try to

improve the interface quality and increase electrostatic control. However, polymer-based dielectrics are limited by the maximum temperature they can withstand, and high- $\kappa$ dielectrics have been observed to increase surface optical phonon scattering. Recently, the potential of 2D materials as dielectrics has been realized<sup>29</sup> in the form of 2D heterostructures. The lack of dangling bonds at the interface of these 2D heterostructures, as well as their small lattice mismatch, reduces possible scattering sources, resulting in better device performance. Additionally, these 2D dielectrics have the potential to tune the electronic properties of their neighboring layer, through either interfacial charge transfer<sup>30</sup> or proximity effects. Efforts toward the high-quality epitaxial growth of these heterostructures have been realized for particular 2D heterostructures such as Janus MoSSe<sup>31</sup> and WSe<sub>2</sub>-MoS<sub>2</sub> lateral p-n junctions.32

GaS, a group III–VI monochalcogenide (MX, M = Ga, In; X = S, Se, Te), is a wide-bandgap semiconductor ( $E_g = 2-3.05$

Received: March 4, 2025 Revised: May 5, 2025 Accepted: May 26, 2025 Published: June 6, 2025

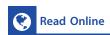

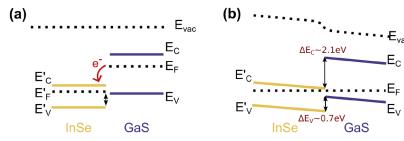

Figure 1. Band alignment of InSe and GaS (a) before and (b) after contact.

eV for decreasing thickness) mainly studied for its uses in optoelectronics.  $^{33-37}$  Recently, the potential of GaS as a dielectric was proven by Shin et al.,  $^{38}$  with their  $\rm GaS/MoS_2$ top-gated heterostructures exhibiting low subthreshold swing and better mobility than bare MoS<sub>2</sub>. However, as aforementioned, MoS2's large effective mass makes it less appealing for high-performance FETs. InSe, a fellow layered semiconductor, with an effective mass four times smaller than that of MoS2, has already been shown to possess a mobility of 1000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature, <sup>26</sup> making it a better candidate for an active channel material.

In this paper, we explore the role of metal contact with GaS on the device performance of InSe/GaS heterostructures. When joined together, these semiconductors form a type II staggered band alignment (Figure 1). 39-42 Because the Fermi level of GaS lies slightly higher than that of InSe, electrons will flow from GaS to InSe until equilibrium is reached (Figure 1b). This accumulation of carriers in InSe, as well as the cleaner interface provided by the absence of dangling bonds and small lattice mismatch, should in theory lead to a higher field-effect mobility. However, we find that this is only the case when the heterostructures are aligned such that the GaS is fully encapsulated by the InSe, indicating that metal contact connecting both InSe and GaS facilitates charge transfer from InSe to GaS. At a large gate voltage (>20 V), this leads to major electron trapping at the interface, which leads to decreased current in the InSe layer and larger hysteresis.

# EXPERIMENTAL SECTION

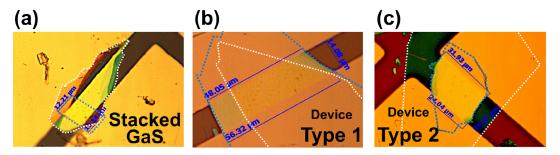

GaS flakes were exfoliated from a bulk crystal by the standard Scotch tape method onto a clean, highly doped Si substrate with a 300 nm SiO<sub>2</sub> capping layer. Samples were then annealed for 1 h at 200 °C under vacuum to remove any tape residue. To form the various heterostructures presented in this paper, a polydimethylsiloxane stamp on a glass slide was used to pick up exfoliated InSe nanoflakes and then stacked on top of the desired GaS flake. InSe flakes were selected to be either larger or smaller in area than the GaS flake. Hereinafter, devices with GaS fully encapsulated by InSe will be referred to as type 1 devices, and devices with GaS not fully covered by the InSe and touching the metal pads will be referred to as type 2 devices. A third device structure, with the InSe/GaS heterostructure contacted by one pad and bare InSe contacting the other pad, was also made to explore the effect of metal contact on the GaS on the performance of our FETs. However, we will not include this device in our main discussion. A total of at least eight devices were created for each device type, and hereafter, when stating a device metric, it is assumed that it is taken to be the average taken from these devices. The transfer curves and device metrics can be found in Sections S3 and S4, Figures S5b and S6b.

To define metal contacts, a copper grid was used as a shadow mask, and e-beam evaporation was used to deposit 30 nm of titanium (Ti) and 60 nm of nickel (Ni). The resulting heterostructures were then annealed again under the aforementioned conditions to improve the InSe/GaS and Ti/heterostructure interface.

A micro-Raman scattering experiment was conducted at room temperature using a Horiba Jobin Yvon LabRam HR800 spectrometer equipped with a carrier coupled device detector and two grating systems (600 and 1800 lines/mm). A He–Ne laser ( $\lambda$  = 632.8 nm) was used with an Olympus optical microscope, BH-2. The laser power used was 17 mW with a spot size of 1  $\mu$ m<sup>2</sup>. The calibration of the Raman shift was done by using the 520 cm<sup>-1</sup> line of a silicon wafer. The laser was focused on the channel area to verify the phase of our flakes and ensure the quality of the resulting heterostructures was intact after processing.

Electrical measurements were performed at room temperature in a Lakeshore probe station using a custom Labview program for data collection. Output curves sweeping the source-drain voltage from ±1 V were used to characterize the contact behavior (as Ohmic or Schottky) at zero and nonzero gate voltages. Additionally, transfer curves at various gate voltage ranges ( $\pm 20$ ,  $\pm 40$ ,  $\pm 60$  V) were used to explore the hysteretic behavior of our heterostructures. The sourcedrain current was normalized by the width of the transistor to display the current density. This was done to ensure a fairer comparison between devices of different geometries.

The threshold voltage,  $V_{\rm T}$ , defined as the gate voltage needed to turn the device on, is extracted from transfer curves by performing a regression fit in the linear regime of the transfer curves and finding the value of  $V_{\rm g}$  when  $I_{\rm ds}$  is zero.<sup>43</sup> The field-effect mobility,  $\mu$ , is also calculated from the transfer curves by extracting the transconductance,  $g = (dI_{ds}/dV_g)|_{V_{ds}}$ , in the linear regime <sup>44</sup> and plugging it into the expression

$$\mu = \frac{L}{W} \frac{g}{C_{\text{ox}} V_{\text{ds}}} \tag{1}$$

where L is the channel length, W is the channel width,  $C_{\rm ox}$  is the oxide capacitance (1.1 nF/cm<sup>2</sup> for 300 nm SiO<sub>2</sub>), and  $V_{ds}$  is the sourcedrain voltage. It quantifies how easily carriers move in the channel under the application of a gate voltage and provides information about the scattering centers in the channel.

Time-dependent conductance measurements were performed to investigate and compare the time relaxation effects in both types of devices. Low-temperature measurements were conducted on bare InSe and its heterostructures to confirm modulation doping from the GaS layer to the InSe layer. Finally, atomic force microscopy scans were obtained with an Agilent MAC Mode III atomic force microscope using a 4 µm wide Bruker TESPD antimony doped silicon tip. Scans were taken in a direction parallel to the channel at a speed of 256 points per line and 0.1 lines per second. Height profiles were obtained along the channel area to obtain thickness measurements of our flakes (Figures S1 and S2).

# ■ RESULTS AND DISCUSSION

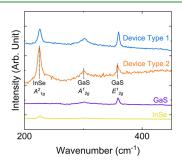

The Raman spectra for our bare InSe and GaS devices as well as their heterostructures can be found in Figure 3. The laser was focused on the channel area of each device, making sure that it overlapped the heterostructure. For  $\gamma$ -InSe, four Raman modes are expected: 45 A<sub>1g</sub><sup>1</sup>, E<sub>2g</sub><sup>1</sup>, A<sub>1g</sub><sup>1</sup>(LO), and A<sub>2g</sub><sup>2</sup>. However, because of the wavelength of our laser, we were able to probe wavenumbers larger than 200 cm<sup>-1</sup> and thus detect only the

Figure 2. Optical images of (a) the premade InSe transistor with GaS stacked on top of it, (b) an example of a type 1 device, and (c) an example of a type 2 device. The blue dotted line marks the InSe flake, and the white dotted line marks the GaS flake in these images.

last mode. Our bare InSe devices display the characteristic A<sub>1g</sub> mode at 226 cm<sup>-1</sup>, and the peak remains for the two device types presented in this paper.

Bulk  $\beta$ -GaS has peaks at 187, 289, and 368 cm<sup>-1</sup> corresponding to the  $A_{1g}^1$ ,  $E_{2g}^1$  and  $A_{1g}^2$  modes.<sup>46</sup> Our bare GaS display peaks at 302 and 359 cm<sup>-1</sup>, blue-shifted and redshifted compared to the  $E^1_{2g}$  and  $A^2_{1g}$  modes, respectively, which is expected as GaS is peeled to thinner layers. These peaks are still detectable in the heterostructures; thus, we can conclude that no major structural changes come about when InSe is placed on top of GaS.

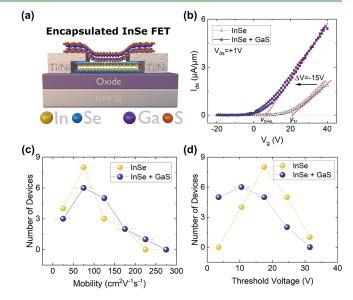

A multilayer GaS flake was stacked on top of a premade InSe transistor (Figures 2a and 4a) to investigate its effect on InSe.

Figure 3. Raman spectra of type 1 and type 2 devices as well as bare GaS and InSe FETs.

The transfer curve of this device before and after the GaS stacking (Figure 4b) shows a clear shift in threshold voltage to the left, indicative of the electron transfer from the GaS to the InSe layer. This is seen across multiple devices, with the average threshold voltage decreasing from 20  $\pm$  1 to 10  $\pm$  2 V upon stacking of GaS on the premade InSe device. The increase in the field-effect mobility from 90  $\pm$  10 to 100  $\pm$  20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> after GaS stacking is within the standard deviation of the bare InSe mobility, suggesting the increase in mobility to be a minor effect. Multiple premade InSe devices were stacked with GaS flakes, and the change in their mobility (Figure 4c) and threshold voltage shifts (Figure 4d) confirm our hypothesis on charge transfer from GaS to InSe and the relatively minor effect of GaS encapsulation on the InSe layer's mobility. The variance in the mobility and threshold voltage in our devices can be attributed to the variance in material thickness<sup>33,49-53</sup> and defect density<sup>54</sup> present in both InSe and GaS flakes.

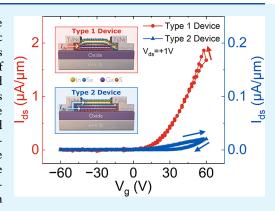

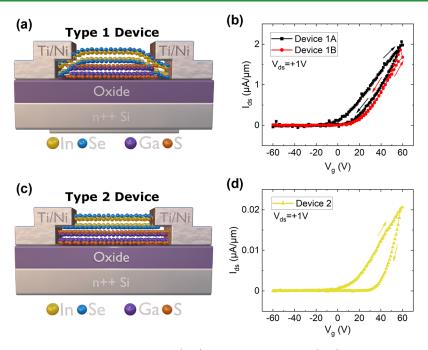

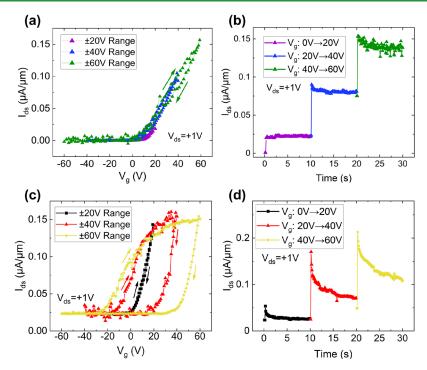

Figure 5b,d shows the representative transfer curves for the two device types examined in this paper with the GaS layer underneath InSe. For this measurement, the gate voltage was swept from 0 to -60 V, back to 0 V, up to +60 V (up-sweep),

Figure 4. (a) Schematic cross-section view of a GaS-capped InSe FET. (b) Transfer curve of InSe FET before and after capping with GaS. Counts of (c) mobility and (d) threshold voltages of InSe FET before and after encapsulating with GaS.

and back again to 0 V (down-sweep) while a constant  $V_{ds} = +1$ V was applied between the source and the drain. All devices exhibit clear n-type behavior, as expected for standalone InSe and GaS FETs (Figures S3 and S4), and a similar subthreshold swing to that of bare InSe (4-10 V/dec). However, the mobility, on-current, and degree of hysteresis are different for each device type.

The average mobilities of type 1 and 2 devices are  $30 \pm 8$ and  $20 \pm 5$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, respectively, much lower than the mobility of bare InSe and GaS-capped InSe FETs. Note that these values are smaller if only considering the up-sweep and larger if only considering the down-sweep. This suggests that the discharging of the InSe layer during the down-sweep is more efficient than the charging during the up-sweep. While both structures display larger hysteresis and smaller oncurrents than the GaS-stacked InSe FETs, type 1 devices show a smaller average threshold voltage  $(14 \pm 4 \text{ V})$  than bare InSe, similar to the GaS-stacked InSe FETs. We attribute the difference in mobility, hysteresis, and on-current between the GaS-capped InSe FET and type 1,2 devices to the lack of direct contact between the GaS layer and the oxide in the GaScapped InSe FET.

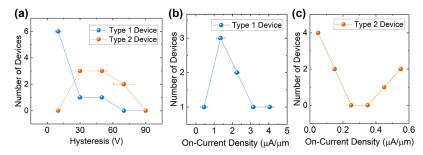

As seen from Figure 6, type 1 device samples on average have higher on-currents (1.9  $\pm$  0.4  $\mu$ A/ $\mu$ m compared to 0.2  $\pm$  $0.1 \mu A/\mu m$ ) and considerably smaller hysteresis than type 2

Figure 5. Cross section and transfer curve of the type 1 device (a, b) and the type 2 device (c, d).

Figure 6. (a) Number of devices measured with a given hysteresis for type 1 and 2 devices. On-current distribution for type 1 (b) and type 2 (c)

device samples (20  $\pm$  6 V compared to 50  $\pm$  6 V). Since the only difference between these two devices is whether the GaS is in contact with the metal, our results suggest that the hysteresis and the decrease in on-current and mobility are caused by current injection into the GaS layer through the metal contacts. Hysteresis is a common phenomenon in FETs made from 2D heterostructures, 55-57 but it is usually attributed to charge transfer and/or trapping induced by the application of a large gate voltage. In the case where the heterostructure consists of a 2D semiconductor and a large bandgap insulator (e.g., hBN), the charge trapping mainly occurs through electron tunneling. 58,59 When the heterostructure consists of a 2D semiconductor (InSe in our case) and another 2D semiconductor with a larger bandgap (GaS in our case), the drastic band bending of the wider bandgap semiconductor by the gate voltage can result in the formation of a triangular potential well at the interface between the widebandgap semiconductor (GaS) and the dielectric (SiO<sub>2</sub>) on the substrate that acts as a charge trapping layer. A similar situation was discussed in our prior study of the InSe/GaSe interface, where the barrier of GaSe was lower and the hysteresis was more severe.<sup>30</sup> The presence of this extra current pathway splits the source-drain current into two and results in a decrease in on-current in type 2 devices. The charges flowing through the GaS can also be trapped within

the layer, which exacerbates the hysteresis observed in type 2 devices. Moreover, it has been reported that direct contact between metal and semiconductor can induce surface phonons that decrease the mobility <sup>34,60,61</sup> and could explain the decrease in mobility of type 2 devices.

Though GaS and Ti make a Schottky contact with a potential barrier of about 2 eV, the thickness of the GaS flakes used in this paper is at most 10 nm, making the width of this triangular potential small enough that tunneling from the metal to the GaS can occur at sufficiently high gate voltages. This results in the range-dependent hysteresis: as the gate voltage is swept from 0 to  $-V_{\rm g}$ , the electron trap states in GaS start to deplete, with more traps depleted if a more negative  $V_{g,max}$  is swept (Figure 7c). These positively charged traps make the potential seen by the InSe more positive than the applied  $V_g$ , hence the turning on of the device at negative  $V_g$ . As  $V_g$  is swept to more positive  $V_g$ , the traps in GaS begin to charge up, offsetting some of the current flowing into the InSe layer. Note that when the GaS layer is not in direct contact with the metal contact (type 1 device), the charging/discharging speed of the GaS layer is much slower than the case where the charging/ discharging can go through metal contacts (type 2 device). This results in the type 1 devices responding to the gate voltage change mainly through the InSe layer, behaving more like bare InSe FETs. For type 2 devices where the charging of

Figure 7. (a)/(c) Example transfer curves and (b)/(d) time-dependent conductance measurements of type 1 and type 2 devices.

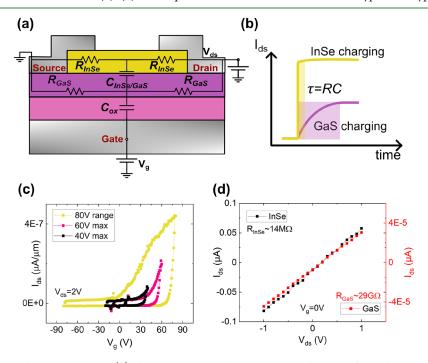

Figure 8. (a) Equivalent circuit for type 2 devices. (b) Illustrative source—drain current as a function of time for InSe (yellow) and GaS (purple) FETs upon sudden turning on the gate voltage. (c) Transfer curve of the bare GaS FET. (d) Current—voltage curve of the bare InSe (red) and GaS (black) FETs.

the GaS layer can go through the source/drain metal contacts, the time constant for the GaS layer's charging/discharging is still much longer than the InSe layer (see Figure 8 and related discussion), giving rise to the strong hysteresis in these devices.

To further test the role of the GaS layer on the electron flow through these heterostructures, time-dependent conductance measurements were taken for each device type. A constant source—drain voltage of +1 V was applied across the channel, while the gate voltage was increased from 0 to +60 V and back

down to 0 V in 20 V increments. Type 1 devices stabilize very quickly (Figure 7b) at low gate voltages, as evident from the small time decay when going from 0 to 20 V, but experience a decay when biased to higher gate voltages. In contrast, type 2 devices exhibit a clear time relaxation effect even at low gate voltages (Figure 7d). Recall, type 2 devices have GaS making contact with the source and drain pads, whereas type 1 devices have GaS fully encapsulated by InSe, with the metal pads only contacting the InSe. As a result, the current in type 1 devices is

limited to the InSe flake, while in type 2 devices, the current is divided between InSe and GaS flakes.

We can model this system as an RC circuit (Figure 8a), with the number of resistors determined by the number of semiconductors contacting the metal. For type 1 devices, the relaxation time,  $\tau$ , is determined simply by the resistance of the InSe layer and the equivalent capacitance of the circuit,  $C_{\rm eq} = (C_{\rm InSe/GaS}^{-1} + C_{\rm ox}^{-1})^{-1}$ , which is dominated by the capacitance of the SiO<sub>2</sub> since the InSe and GaS layers are much thinner. Taking the average resistance of ungated InSe,  $R = 14 \text{ M}\Omega$ , the equivalent capacitance  $C_{\rm eq} = 11~{\rm nF/cm^2}$ , and the area of the InSe flake to be  $A_{\rm InSe} = 2.8 \times 10^{-5}~{\rm cm^2}$ , the resultant time constant for InSe is  $\tau_{InSe}$  = 4  $\mu s$ . In other words, InSe charges and discharges very quickly (Figure 8b).

In contrast, contact with GaS in type 2 devices leads to an additional resistor in the circuit that provides the current with an extra pathway to flow. This resistor,  $R_{GaS}$ , is several orders of magnitude larger than  $R_{InSe}$  (Figure 8d), especially at higher gate voltages (Figure 8c), and connects the contacts to the equivalent capacitor created by the InSe and GaS layers, C<sub>InSe/GaS</sub>. The resistance of the GaS layer can be taken from output curves (red curve in Figure 8d), with  $R_{GaS} = 29$  G $\Omega$ . The capacitance of the InSe and GaS layers can be calculated using the formula for a parallel capacitor with a dielectric constant of  $\epsilon$  = 8 and using the average thickness of type 2 devices,  $d_{\text{InSe}} = 30 \text{ nm}$  and  $d_{\text{GaS}} = 10 \text{ nm}$ , respectively, and we obtain  $C_{\text{InSe/GaS}} = (C_{\text{InSe}}^{-1} + C_{\text{GaS}}^{-1})^{-1} = 10^3 \text{ nF/cm}^2$ . Thus, the RC time constant for the GaS and InSe bilayer is  $\tau_{InSe/GaS}\approx$  0.8 s, which is closer in magnitude to the discharge time that we obtained in our time-dependent conductance measurements. This current splitting between the GaS and InSe layers explains the increase in hysteresis and smaller on-current for type 2 devices. In GaS-capped InSe FETs, the lack of connection between GaS and  $C_{InSe/GaS}$  leads the channel to have a relaxation time of bare InSe, and hence the smaller hysteresis and larger on-current in these devices.

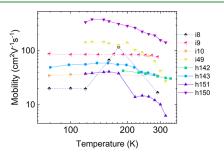

To investigate the mobility of our heterostructure devices and bare InSe FETs, we obtain transfer curves at temperatures ranging from 77 to 320 K (Figures S7 and S8). A plot of the extracted mobility as a function of temperature is present in Figure 9. The half-filled symbols connected with dotted lines in Figure 9 represent the bare InSe FETs, while the filled symbols connected by a solid line represent the type 1 device heterostructures. The variation in mobility from device to device can be attributed to variations in the InSe film thickness. The InSe thicknesses in devices i8, i9, i10, and i49 are 11, 50, 20, and 14 nm (Figure S1). The room-temperature mobility

Figure 9. Plot of mobility as a function of temperature for our type 1 devices and bare InSe FETs. The half-filled symbols connected with dotted lines represent the bare InSe devices, while the filled symbols connected with a solid line represent our type 1 devices.

seems to increase as the thickness increases from 11 to 50 nm, consistent with previous InSe transistors on SiO<sub>2</sub>. 62 This increase in mobility with increasing thickness has been attributed to the screening of charge traps at the semiconductor/oxide interface.<sup>63</sup>

The relationship between flake thickness and mobility is not as trivial in our heterostructured devices because of the variance in both InSe and GaS thickness. Nonetheless, we observe an increase in the room-temperature mobility with a decreasing GaS thickness. The device with the highest roomtemperature mobility is h151, with InSe and GaS thicknesses of 20 and 10 nm, respectively. Meanwhile, the device with the lowest room-temperature mobility is h150, which has InSe and GaS thicknesses of 37 and 16 nm, respectively. Since we know from our study of bare InSe FETs that the mobility of InSe increases with layer thickness, we can conclude that the decrease in mobility in our heterostructure devices originates from the increasing thickness in the GaS layer. This phenomenon has also been reported in AlGaN/GaN heterostructures, where the increase in AlGaN thickness resulted in an increase of the mobility up to a certain AlGaN thickness, after which it declined. 66 This is attributed to a decrease in the barrier height between the two heterostructures<sup>67</sup> as well as the increase in alloy disorder and interface roughness scattering<sup>68,69</sup> with increasing AlGaN thickness. Similar conclusions can be drawn with our InSe/ GaS heterostructures. With increasing thickness, the bandgap of GaS decreases and thus so does the conduction band edge difference between it and InSe. This can result in a smaller barrier height at the interface, which can allow electron states in the GaS layer to penetrate into the InSe. Additionally, the increase in defect states in thicker GaS flakes can also lead to a decrease in mobility with increasing GaS thickness.

The mobility of FETs is affected by different scattering mechanisms in different temperature regimes. At low T, charge impurity scattering and acoustic phonon scattering are the dominant scattering mechanisms. They manifest themselves with a positive power law dependence of the form  $\mu \propto T^{\gamma}$ , where  $\gamma = +1.5$ . Conversely, at high T, the mobility is limited by optical phonon scattering, where  $\gamma = -1.5$ . As a result, the log-plot of mobility as a function of temperature has a positive slope for low T and a negative slope for high T. However, both our bare and heterostructure devices deviate from these theoretical values.<sup>70</sup> Our thinner InSe flakes (i8 and i49) display a larger temperature dependence than the thicker flakes (i10 and i9), particularly at temperatures above 180 K, potentially due to the increased effect of optical phonons that the thinner flakes are not able to screen. By taking the linear fit from the peak of the graph (T = 180 K) to our highest temperature (T = 320 K), we obtain  $\gamma$  values of -4.1 and -3.2for i8 and i49, respectively. This value is an order of magnitude smaller in our thicker InSe samples,  $\gamma = -0.1$ , signaling the larger impact of phonon scattering in thinner samples than in thicker ones. A similar trend is present in our heterostructures, where  $\gamma$  ranges from -1 to 2.5, with the smallest value coming from the device with thicker GaS and InSe flakes.

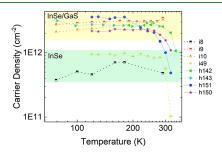

When examining the carrier density of our devices, we note a larger average current density in our heterostructures than in bare InSe FETs, even at low temperatures, signifying doping in InSe from the GaS layer. Threshold voltages for four bare InSe devices and four type 1 device samples were obtained at different temperatures, from 77 to 320 K, and used to calculate their carrier density. Taking the carrier density to be  $n = C_{ox}(V_{\sigma})$

$-V_{\rm Th}$ ), where  $C_{\rm ox}$  is the capacitance of the silicon oxide (1.15)  $\mu F/\text{cm}^2$  for 300 nm SiO<sub>2</sub>),  $V_g$  is the applied gate voltage, and  $V_{Th}$  is the threshold voltage of the device, we plot it against temperature at  $V_{\sigma} = 50 \text{ V}$  to obtain Figure 10. The average carrier density of type 1 devices is well above 10<sup>12</sup> cm<sup>-2</sup> and does not drop drastically at high temperatures, indicative of a doping of approximately  $1 \times 10^{12}$  cm<sup>-2</sup>.

Figure 10. Carrier density for type 1 device samples and bare InSe devices as a function of temperature.

In contrast, the carrier density of bare InSe ranges from 4 ×  $10^{12}$  to  $3 \times 10^{11}$  cm<sup>-2</sup>. This spread in carrier density can be attributed to the varying thicknesses of the InSe flakes measured, with the higher carrier density corresponding to the thicker InSe flake (50 nm) and the lowest carrier density being that of the thinnest InSe flake (11 nm). Type 1 devices, on the other hand, tend to have a carrier density much higher than that of the thin InSe transistors, regardless of InSe and GaS thickness. This can be used to increase the carrier concentration in thinner InSe samples, which we know suffer from low electron concentrations (i8 and i49 in Figure 10), to achieve doping concentrations closer to what is obtainable in thicker InSe flakes, with the additional benefit of decreasing charge scattering at low T.

### CONCLUSIONS

In this paper, we have studied the electron transport properties of InSe/GaS heterostructures, wherein GaS is fully encapsulated by InSe (type 1 device) and GaS is contacting both pads (type 2 device). We have found that out of both devices, type 1 devices display the smallest hysteresis with the largest oncurrent and mobility. We attribute the lower performance of the type 2 device to current splitting between the InSe and GaS layers both making contact with the metal pads and its slow time constant. Additionally, we have shown the potential of GaS to modulate the carrier density of InSe and increase the mobility at low temperatures. This study can aid in the design and understanding of future 2D heterostructures with the desired electronic properties.

### ASSOCIATED CONTENT

# Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.5c04399.

> AFM height profiles for thickness determination; bare InSe and GaS FET transfer characteristics; transfer characteristics and device metrics for type1 devices; transfer characteristics and device metrics for type2 devices; temperature-dependent transfer curves for bareInSe and type 1 devices; and additional supporting figures and tables (PDF)

#### AUTHOR INFORMATION

#### Corresponding Authors

Julian Ignacio Deagueros - Department of Physics, Case Western Reserve University, Cleveland, Ohio 44106, United States; orcid.org/0000-0003-3511-6954; Email: julian.deagueros@case.edu

Xuan P. A. Gao - Department of Physics, Case Western Reserve University, Cleveland, Ohio 44106, United States; orcid.org/0000-0002-7045-9656; Email: xuan.gao@ case.edu

#### Authors

Min Gao - Department of Physics, Case Western Reserve University, Cleveland, Ohio 44106, United States Alice Cai - Department of Physics, Case Western Reserve University, Cleveland, Ohio 44106, United States; orcid.org/0009-0001-0983-623X

Xiaotong Li - Department of Physics, Case Western Reserve University, Cleveland, Ohio 44106, United States

Rajesh Kumar Ulaganathan - Centre for Nanotechnology, Indian Institute of Technology Roorkee, Roorkee 247667, *India;* orcid.org/0000-0001-8886-6332

Shankar Mani – Institute of Physics, Academia Sinica, Taipei 11529, Taiwan

Raman Sankar – Institute of Physics, Academia Sinica, Taipei 11529, Taiwan; orcid.org/0000-0003-4702-2517

Hatsuo Ishida - Department of Macromolecular Science and Engineering, Case Western Reserve University, Cleveland, Ohio 44106, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.5c04399

The authors declare no competing financial interest.

#### **ACKNOWLEDGMENTS**

X.P.A.G. acknowledges the support from NSF (DMR-1607631) and a generous grant from the Expanding Horizons Initiative (EHI), College of Arts and Sciences, Case Western Reserve University. R.S. acknowledges the financial support provided by the Ministry of Science and Technology in Taiwan under Project No. NSTC (113-2124-M-001-045-MY3 and 113-2124-M-001-003), financial support from the Center of Atomic Initiative for New Materials (AI-Mat), National Taiwan University (Project No. 113L900801), and Academia Sinica for the budget of AS-iMATE-113-12.

#### REFERENCES

- (1) Das, S.; Robinson, J. A.; Dubey, M.; Terrones, H.; Terrones, M. Beyond Graphene: Progress in Novel Two-Dimensional Materials and van der Waals Solids. Annu. Rev. Mater. Res. 2015, 45, 1-27.

- (2) Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. ACS Nano 2014, 8, 1102-1120.

- (3) Roy, T.; Tosun, M.; Kang, J. S.; Sachid, A. B.; Desai, S. B.; Hettick, M.; Hu, C. C.; Javey, A. Field-Effect Transistors Built from All Two-Dimensional Material Components. ACS Nano 2014, 8,

- (4) Bhimanapati, G. R.; et al. Recent Advances in Two-Dimensional Materials beyond Graphene. ACS Nano 2015, 9, 11509-11539.

- (5) Chhowalla, M.; Shin, H. S.; Eda, G.; Li, L.-J.; Loh, K. P.; Zhang, H. The Chemistry of Two-Dimensional Layered Transition Metal Dichalcogenide Nanosheets. Nat. Chem. 2013, 5, 263-275.

- (6) Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

- (7) Lotsch, B. V. Vertical 2D Heterostructures. *Annu. Rev. Mater. Res.* 2015, 45, 85–109.

- (8) Ibarra-Hernández, W.; Elsayed, H.; Romero, A. H.; Bautista-Hernández, A.; Olguín, D.; Cantarero, A. Electronic Structure, Lattice Dynamics, and Optical Properties of a Novel van der Waals Semiconductor Heterostructure: InGaSe<sub>2</sub>. *Phys. Rev. B* **2017**, *96*, No. 035201.

- (9) Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Castro Neto, A. H. 2D Materials and van der Waals Heterostructures. *Science* **2016**, 353, No. aac9439.

- (10) Wang, H.; Liu, F.; Fu, W.; Fang, Z.; Zhou, W.; Liu, Z. Two-Dimensional Heterostructures: Fabrication, Characterization, and Application. *Nanoscale*. **2014**, *6*, 12250–12272.

- (11) Huang, W.; Gan, L.; Li, H.; Ma, Y.; Zhai, T. 2D Layered Group IIIA Metal Chalcogenides: Synthesis, Properties and Applications in Electronics and Optoelectronics. *CrystEngComm.* **2016**, *18*, 3968–3984.

- (12) Xu, K.; Yin, L.; Huang, Y.; Shifa, T. A.; Chu, J.; Wang, F.; Cheng, R.; Wang, Z.; He, J. Synthesis, Properties and Applications of 2D Layered  $M^{III}X^{VI}$  (M = Ga, In; X = S, Se, Te) Materials. *Nanoscale*. **2016**, *8*, 16802–16818.

- (13) Geim, A. K.; Grigorieva, I. V. Van der Waals Heterostructures. *Nature.* **2013**, 499, 419–425.

- (14) Li, M.-Y.; Chen, C.-H.; Shi, Y.; Li, L.-J. Heterostructures Based on Two-Dimensional Layered Materials and Their Potential Applications. *Mater. Today.* **2016**, *19*, 322–335.

- (15) Huang, L.-Y.; et al. Area-Selective Growth of Two-Dimensional Mono- and Bilayer WS<sub>2</sub> for Field Effect Transistors. *ACS Mater. Lett.* **2023**, *5*, 1760–1766.

- (16) Cui, X.; et al. Multi-Terminal Transport Measurements of MoS<sub>2</sub> Using a van der Waals Heterostructure Device Platform. *Nat. Nanotechnol.* **2015**, *10*, 534–540.

- (17) Mathew, R.; Ajayan, J. Material Processing, Performance and Reliability of MoS<sub>2</sub> Field Effect Transistor (FET) Technology- A Critical Review. *Mater. Sci. Semicond. Process.* **2023**, *160*, No. 107397.

- (18) Li, X.; Zhu, H. Two-Dimensional MoS<sub>2</sub>: Properties, Preparation, and Applications. *J. Materiomics.* **2015**, *1*, 33–44.

- (19) Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. *Proc. Nat. Acad. Sci.* **2005**, *102*, 10451–10453.

- (20) Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? *Nano Lett.* **2011**, *11*, 3768–3773.

- (21) Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge Trapping at the MoS<sub>2</sub>-SiO<sub>2</sub> Interface and Its Effects on the Characteristics of MoS<sub>2</sub> Metal-Oxide-Semiconductor Field Effect Transistors. *Appl. Phys. Lett.* **2015**, *106*, 103109.

- (22) Xu, Q.; Sun, Y.; Yang, P.; Dan, Y. Density of Defect States Retrieved from the Hysteretic Gate Transfer Characteristics of Monolayer  $MoS_2$  Field Effect Transistors. *AIP Adv.* **2019**, *9*, No. 015230.

- (23) Shu, J.; Wu, G.; Guo, Y.; Liu, B.; Wei, X.; Chen, Q. The Intrinsic Origin of Hysteresis in MoS<sub>2</sub> Field Effect Transistors. *Nanoscale.* **2016**, *8*, 3049–3056.

- (24) Lee, K.; Lee, H.; Kim, Y.; Choi, J.; Ahn, J.-P.; Shin, D. H.; Cho, Y.-H.; Jang, H.-k.; Lee, S. W.; Shin, J.; Ji, H.; Kim, G.-T. Real-Time Effect of Electron Beam on MoS<sub>2</sub> Field-Effect Transistors. *Nat. Nanotechnol.* **2020**, *31*, 455202.

- (25) Vu, Q. A.; Fan, S.; Lee, S. H.; Joo, M.-K.; Yu, W. J.; Lee, Y. H. Near-Zero Hysteresis and near-Ideal Subthreshold Swing in h-BN Encapsulated Single-Layer MoS<sub>2</sub> Field-Effect Transistors. 2D Mater. **2018**, 5, No. 031001.

- (26) Sucharitakul, S.; Goble, N. J.; Kumar, U. R.; Sankar, R.; Bogorad, Z. A.; Chou, F.-C.; Chen, Y.-T.; Gao, X. P. A. Intrinsic

- Electron Mobility Exceeding  $10^3 \text{ cm}^2/(\text{V s})$  in Multilayer InSe FETs. *Nano Lett.* **2015**, *15*, 3815–3819.

- (27) Feng, W.; Zheng, W.; Chen, X.; Liu, G.; Hu, P. Gate Modulation of Threshold Voltage Instability in Multilayer InSe Field Effect Transistors. *ACS Appl. Mater. & Interfaces.* **2015**, *7*, 26691–26695.

- (28) Wang, Y.; Huang, X.; Li, T.; Li, L.; Guo, X.; Jiang, P. Polymer-Based Gate Dielectrics for Organic Field-Effect Transistors. *Chem. Mater.* **2019**, *31*, 2212–2240.

- (29) Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; Taniguchi, T.; Kim, P.; Shepard, K. L.; Hone, J. Boron Nitride Substrates for High-Quality Graphene Electronics. *Nat. Nanotechnol.* **2010**, *5*, 722–726.

- (30) Kumar, A. S.; Wang, M.; Li, Y.; Fujita, R.; Gao, X. P. A. Interfacial Charge Transfer and Gate-Induced Hysteresis in Monochalcogenide InSe/GaSe Heterostructures. *ACS Appl. Mater. & Interfaces.* **2020**, *12*, 46854–46861.

- (31) Lu, A.-Y.; et al. Janus Monolayers of Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2017**, *12*, 744–749.

- (32) Li, M.-Y.; Shi, Y.; Cheng, C.-C.; Lu, L.-S.; Lin, Y.-C.; Tang, H.-L.; Tsai, M.-L.; Chu, C.-W.; Wei, K.-H.; He, J.-H.; Chang, W.-H.; Suenaga, K.; Li, L.-J. Epitaxial Growth of a Monolayer WSe<sub>2</sub>-MoS<sub>2</sub> Lateral p-n Junction with an Atomically Sharp Interface. *Science.* 2015, 349. 524–528.

- (33) Gutiérrez, Y.; Giangregorio, M. M.; Dicorato, S.; Palumbo, F.; Losurdo, M. Exploring the Thickness-Dependence of the Properties of Layered Gallium Sulfide. *Frontiers Chem.* **2021**, *9*, No. 781467.

- (34) Chen, T.; Lu, Y.; Sheng, Y.; Shu, Y.; Li, X.; Chang, R.-J.; Bhaskaran, H.; Warner, J. H. Ultrathin All-2D Lateral Graphene/GaS/Graphene UV Photodetectors by Direct CVD Growth. ACS Appl. Mater. & Interfaces. 2019, 11, 48172–48178.

- (35) Mancini, A. M.; Micocci, G.; Rizzo, A. New Materials for Optoelectronic Devices: Growth and Characterization of Indium and Gallium Chalcogenide Layer Compounds. *Mater. Chem. Phys.* **1983**, 9, 29–54.

- (36) Williams, R. H.; Higginbotham, I. G.; Whitaker, M. A. B. Adsorption Anisotropy in Layer Chalcogenides. *J. Phys. C: Solid State Phys.* **1972**, *5*, L191.

- (37) Zhuang, H. L.; Hennig, R. G. Single-Layer Group-III Monochalcogenide Photocatalysts for Water Splitting. *Chem. Mater.* **2013**, 25, 3232–3238.

- (38) Shin, G. H.; Lee, G.-B.; An, E.-S.; Park, C.; Jin, H. J.; Lee, K. J.; Oh, D. S.; Kim, J. S.; Choi, Y.-K.; Choi, S.-Y. High-Performance Field-Effect Transistor and Logic Gates Based on GaS-MoS<sub>2</sub> van Der Waals Heterostructure. ACS Appl. Mater. & Interfaces. 2020, 12, 5106-5112.

- (39) Manfredotti, C.; Murri, R.; Rizzo, A.; Vasanelli, L. Hall Effect in N-Type GaS. *Solid State Commun.* 1976, 19, 339–342.

- (40) Rizzo, A.; De Blasi, C.; Ga, S.; Micocci, G.; Ruggiero, L.; Tepori, A. Electrical Properties of N-Type GaS Single Crystals. *Solid State Commun.* **1981**, *40*, 641–644.

- (41) Mudd, G. W.; Svatek, S. A.; Ren, T.; Patanè, A.; Makarovsky, O.; Eaves, L.; Beton, P. H.; Kovalyuk, Z. D.; Lashkarev, G. V.; Kudrynskyi, Z. R.; Dmitriev, A. I. Tuning the Bandgap of Exfoliated InSe Nanosheets by Quantum Confinement. *Adv. Mater.* **2013**, *25*, 5714–5718.

- (42) Mudd, G. W.; Molas, M. R.; Chen, X.; Zólyomi, V.; Nogajewski, K.; Kudrynskyi, Z. R.; Kovalyuk, Z. D.; Yusa, G.; Makarovsky, O.; Eaves, L.; Potemski, M.; Fal'ko, V. I.; Patanè, A. The Direct-to-Indirect Band Gap Crossover in Two-Dimensional van der Waals Indium Selenide Crystals. *Sci. Rep.* **2016**, *6*, 39619.

- (43) Ortiz-Conde, A.; García Sánchez, F. J.; Liou, J. J.; Cerdeira, A.; Estrada, M.; Yue, Y. A Review of Recent MOSFET Threshold Voltage Extraction Methods. *Microelectron. Reliab.* **2002**, *42*, 583–596.

- (44) Mitta, S. B.; Choi, M. S.; Nipane, A.; Ali, F.; Kim, C.; Teherani, J. T.; Hone, J.; Yoo, W. J. Electrical Characterization of 2D Materials-Based Field-Effect Transistors. 2D Mater. 2021, 8, No. 012002.

- (45) Wu, M.; Xie, Q.; Wu, Y.; Zheng, J.; Wang, W.; He, L.; Wu, X.; Lv, B. Crystal Structure and Optical Performance in Bulk γ-InSe Single Crystals. *AIP Adv.* **2019**, *9*, No. 025013.

- (46) Yang, S.; Li, Y.; Wang, X.; Huo, N.; Xia, J.-B.; Li, S.-S.; Li, J. High Performance Few-Layer GaS Photodetector and Its Unique Photo-Response in Different Gas Environments. *Nanoscale.* **2014**, *6*, 2582–2587.

- (47) Hu, P.; Wang, L.; Yoon, M.; Zhang, J.; Feng, W.; Wang, X.; Wen, Z.; Idrobo, J. C.; Miyamoto, Y.; Geohegan, D. B.; Xiao, K. Highly Responsive Ultrathin GaS Nanosheet Photodetectors on Rigid and Flexible Substrates. *Nano Lett.* **2013**, *13*, 1649–1654.

- (48) Late, D. J.; Liu, B.; Matte, H. S. S. R.; Rao, C. N. R.; Dravid, V. P. Rapid Characterization of Ultrathin Layers of Chalcogenides on SiO<sub>2</sub>/Si Substrates. *Adv. Funct. Mater.* **2012**, *22*, 1894–1905.

- (49) Li, S.-L.; Wakabayashi, K.; Xu, Y.; Nakaharai, S.; Komatsu, K.; Li, W.-W.; Lin, Y.-F.; Aparecido-Ferreira, A.; Tsukagoshi, K. Thickness-Dependent Interfacial Coulomb Scattering in Atomically Thin Field-Effect Transistors. *Nano Lett.* **2013**, *13*, 3546–3552.

- (50) Zhang, Y.; Li, H.; Wang, H.; Xie, H.; Liu, R.; Zhang, S.-L.; Qiu, Z.-J. Thickness Considerations of Two-Dimensional Layered Semi-conductors for Transistor Applications. *Sci. Rep.* **2016**, *6*, 29615.

- (51) Li, S.-L.; Komatsu, K.; Nakaharai, S.; Lin, Y.-F.; Yamamoto, M.; Duan, X.; Tsukagoshi, K. Thickness Scaling Effect on Interfacial Barrier and Electrical Contact to Two-Dimensional MoS<sub>2</sub> Layers. *ACS Nano* **2014**, *8*, 12836–12842.

- (52) Lembke, D.; Allain, A.; Kis, A. Thickness-Dependent Mobility in Two-Dimensional MoS<sub>2</sub> Transistors. *Nanoscale.* **2015**, *7*, 6255–6260

- (53) Isakov, I.; Faber, H.; Mottram, A. D.; Das, S.; Grell, M.; Regoutz, A.; Kilmurray, R.; McLachlan, M. A.; Payne, D. J.; Anthopoulos, T. D. Quantum Confinement and Thickness-Dependent Electron Transport in Solution-Processed In<sub>2</sub>O<sub>3</sub> Transistors. *Adv. Electron. Mater.* **2020**, *6*, No. 2000682.

- (54) Smithe, K. K. H.; Suryavanshi, S. V.; Muñoz Rojo, M.; Tedjarati, A. D.; Pop, E. Low Variability in Synthetic Monolayer MoS<sub>2</sub> Devices. *ACS Nano* **2017**, *11*, 8456–8463.

- (55) Li, D.; Wang, X.; Zhang, Q.; Zou, L.; Xu, X.; Zhang, Z. Nonvolatile Floating-Gate Memories Based on Stacked Black Phosphorus—Boron Nitride—MoS<sub>2</sub> Heterostructures. *Adv. Funct. Mater.* **2015**, 25, 7360—7365.

- (56) Park, W.; Jang, H. Y.; Nam, J. H.; Kwon, J.-D.; Cho, B.; Kim, Y. Artificial 2D van der Waals Synapse Devices via Interfacial Engineering for Neuromorphic Systems. *Nanomaterials.* **2020**, *10*, 88.

- (57) Yao, J.; Guo, W.; Liu, Y.; Niu, X.; Li, M.; Wu, X.; Yu, Y.; Ou, T.; Sha, J.; Wang, Y. Gate Induced Charge Transfer and Hysteresis Enlargement in MoS<sub>2</sub>/GeSe<sub>2</sub> Vertical Heterostructures. *J. Mater. Chem. C* **2021**, *9*, 8213–8219.

- (58) Vu, Q. A.; Shin, Y. S.; Kim, Y. R.; Nguyen, V. L.; Kang, W. T.; Kim, H.; Luong, D. H.; Lee, I. M.; Lee, K.; Ko, D.-S.; Heo, J.; Park, S.; Lee, Y. H.; Yu, W. J. Two-Terminal Floating-Gate Memory with van der Waals Heterostructures for Ultrahigh on/off Ratio. *Nat. Commun.* 2016, 7, 12725.

- (59) Lee, G.-H.; Yu, Y.-J.; Lee, C.; Dean, C.; Shepard, K. L.; Kim, P.; Hone, J. Electron Tunneling through Atomically Flat and Ultrathin Hexagonal Boron Nitride. *Appl. Phys. Lett.* **2011**, *99*, 243114.

- (60) Pham, P. V.; Bodepudi, S. C.; Shehzad, K.; Liu, Y.; Xu, Y.; Yu, B.; Duan, X. 2D Heterostructures for Ubiquitous Electronics and Optoelectronics: Principles, Opportunities, and Challenges. *Chem. Rev.* 2022, 122, 6514–6613.

- (61) Fratini, S.; Guinea, F. Substrate-Limited Electron Dynamics in Graphene. *Phys. Rev. B* **2008**, *77*, No. 195415.

- (62) Jiang, J.; Li, J.; Li, Y.; Duan, J.; Li, L.; Tian, Y.; Zong, Z.; Zheng, H.; Feng, X.; Li, Q.; Liu, H.; Zhang, Y.; Ren, T.-L.; Han, L. Stable InSe Transistors with High-Field Effect Mobility for Reliable Nerve Signal Sensing. *npj* 2D Mater. Appl. 2019, 3, 29.

- (63) Lin, M.-W.; Kravchenko, I. I.; Fowlkes, J.; Li, X.; Puretzky, A. A.; Rouleau, C. M.; Geohegan, D. B.; Xiao, K. Thickness-Dependent Charge Transport in Few-Layer MoS<sub>2</sub> Field-Effect Transistors. *Nat. Nanotechnol.* **2016**, *27*, 165203.

- (64) Wasala, M.; Patil, P.; Ghosh, S.; Weber, L.; Lei, S.; Talapatra, S. Role of Layer Thickness and Field-Effect Mobility on Photoresponsivity of Indium Selenide (InSe)-Based Phototransistors. Oxf. Open Mater. Sci. 2021, 1, No. itab010.

- (65) Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- (66) Ibbetson, J. P.; Fini, P. T.; Ness, K. D.; DenBaars, S. P.; Speck, J. S.; Mishra, U. K. Polarization Effects, Surface States, and the Source of Electrons in AlGaN/GaN Heterostructure Field Effect Transistors. *Appl. Phys. Lett.* **2000**, *77*, 250–252.

- (67) Koley, G.; Spencer, M. G. Surface Potential Measurements on GaN and AlGaN/GaN Heterostructures by Scanning Kelvin Probe Microscopy. *J. Appl. Phys.* **2001**, *90*, 337–344.

- (68) Elsass, C. R.; Poblenz, C.; Heying, B.; Fini, P.; Petroff, P. M.; DenBaars, S. P.; Mishra, U. K.; Speck, J. S.; Saxler, A.; Elhamrib, S.; Mitchel, W. C. Influence of Growth Temperature and Thickness of AlGaN Caps on Electron Transport in AlGaN/GaN Heterostructures Grown by Plasma-assisted Molecular Beam Epitaxy. *Jpn. J. Appl. Phys.* **2001**, *40*, 6235.

- (69) Smorchkova, I. P.; Elsass, C. R.; Ibbetson, J. P.; Vetury, R.; Heying, B.; Fini, P.; Haus, E.; DenBaars, S. P.; Speck, J. S.; Mishra, U. K. Polarization-Induced Charge and Electron Mobility in AlGaN/GaN Heterostructures Grown by Plasma-Assisted Molecular-Beam Epitaxy. J. Appl. Phys. 1999, 86, 4520–4526.

- (70) Kaasbjerg, K.; Thygesen, K. S.; Jacobsen, K. W. Phonon-Limited Mobility in n-Type Single-Layer MoS<sub>2</sub> from First Principles. *Phys. Rev. B* **2012**, *85*, No. 115317.